[IMID 2022] SEL, Si CMOS와 OSFET가 통합된 5,291ppi micro OLED 디스플레이 개발

지난 8월 24일부터 26일까지 진행된 IMID 2022에서 Semiconductor Energy Laboratory(이하 SEL)이 Si CMOS와 OSFET이 통합된 AR/VR용 5,291ppi micro OLED 디스플레이를 개발했다고 발표했다.

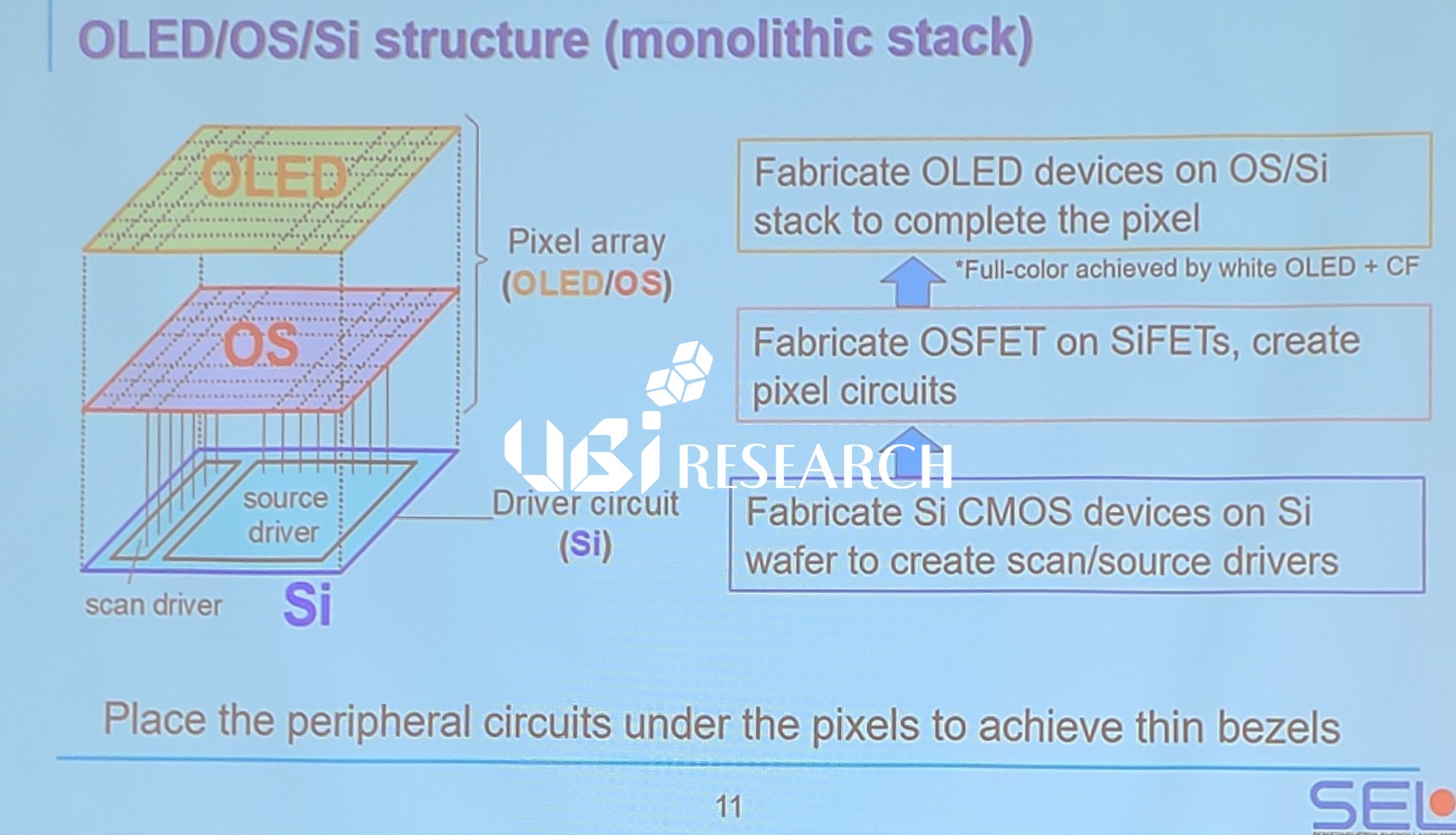

OLED,OS,Si 구조/SEL

SEL에서 발표한 내용에 따르면 기존의 Si FET를 통합하여 높은 화소 밀도의 OLED 디스플레이를 제작할 때 두 가지 문제점이 발생한다. 첫 번째는 소스/게이트 드라이버가 디스플레이 영역 외부에 위치해 베젤 너비가 커지는 것이다. 얇은 베젤 너비는 알맞은 AR/VR 장치 크기를 위한 필수 조건이다. 두 번째는 Si FET의 높은 이동성과 픽셀 간의 균형 문제이다. Micro OLED에 Si FET를 적용하기 위해서는 전류 증가를 억제시키면서 트랜지스터 크기를 줄여야한다.

SEL에서는 이 같은 문제점들을 해결하기 위해서 Si CMOS와 OSFET가 통합된 OLED 마이크로 디스플레이 프로토타입을 제작했다고 밝혔다. SEL에서는 “OSFET의 이동성이 Si FET만큼 높지는 않지만, OLED 장치를 구동하기 충분하다. CMOS위에 OS(OSFET)와 OLED가 합쳐진 OLED/OS/Si 구조를 통해서 베젤 영역의 너비를 최대 40% 줄일 수 있었다. 또 OSFET의 특성 평가에서 딥 블랙 구현 및 저주사율 구동이 가능했으며, 200 nm의 채널길이에서의 양호한 분포도와 항복전압(breakdown voltage) 약 20 V로 White-tandem OLED 소자의 고전압 OLED 구동에 적절하다는 결과가 나타났다” 고 발표했다.

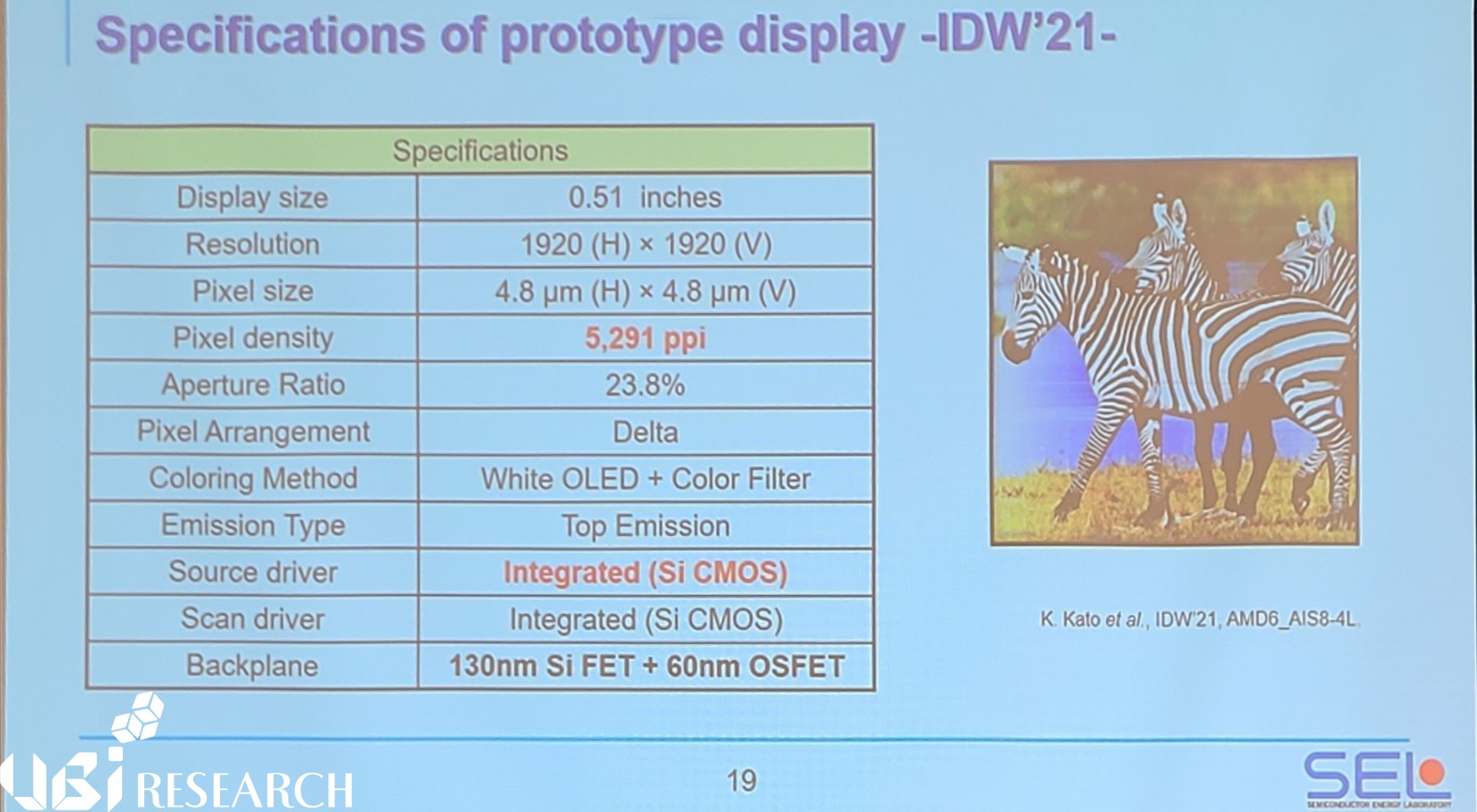

SEL이 발표한 5,291ppi micro OLED display의 사이즈는 0.51인치, 해상도는 1920×1920, 픽셀 사이즈는 4.8×4.8 μm이며, 백플레인은 130 nm Si FET와 60 nm OSFET가 합쳐진 구조이다.

5,291ppi Micro OLED display 스펙/ SEL

2022 Micro-Display 기술 보고서 Sample 보러가기

2022 Micro-Display 기술 보고서 Sample 보러가기